特惠-26考研冲刺

特惠-27考研课

双证-在职硕士

免联考-同等学力

复试分数线

26复试全面指导

模拟复试面试

26考研-全套真题

26考研估分

保研-路线图

27考研-智能择校

27考研-英语测评

27考研-新大纲对比

热门-计算机择校

扫码加入训练营

牢记核心词

学习得礼盒

今天新东方在线考研频道小编为各位考生整理了“2024考研计算机组成原理试题汇总(5)”,相关内容。专业、实用的计算机研究生真题备考内容,能使大家更有效率的掌握相关知识点,避免盲目学!更多计算机研究生真题精彩内容,时刻关注新东方在线考研频道!

2024考研计算机组成原理试题汇总(5)

一、选择题(每个题2分)

11.冯•诺依曼计算机中指令和数据均以二进制形式存放在存储器中,CPU区分它们的依据是

A.指令操作码的译码结果 B.指令和数据的寻址方式

C.指令周期的不同阶段 D.指令和数据所在的存储单元

[答案] C

[解析] 1、指令执行步骤,在取指期间取来的是指令,读数据期间读来的是数据;

2、指令和数据性质上的区别,虽然二者都用二进制表示,但属于完全不同性质的信息,数据是计算机加工处理的“原材料”,指令是告知计算机运行功能和执行步骤的命令类信息。

12.一个C语言程序在一台32位机器上运行。程序中定义了三个变量x、y和z,其中x和z为int型,y为short型。当x = 127,y = -9时,执行赋值语句z = x+y后,x、y和z的值分别是

A.x = 0000007FH,y = FFF9H,z = 00000076H

B.x = 0000007FH,y = FFF9H,z = FFFF0076H

C.x = 0000007FH,y = FFF7H,z = FFFF0076H

D.x = 0000007FH,y = FFF7H,z = 00000076H

[答案] D

[解析] 1、十进制整数到二进制的转换,数据的补码表示;

2、补码加法运算,2两个不同位数的补码数相加时需要进行符号扩展;

X=127,[X]补=0000007FH(32位整数),运算后其值不变

Y=-9,[Y]补=FFF7H (16位整数),运算后其值不变

[Z]补 = [X补+Y补]=0000007FH+FFFFFFF7H=00000076H

3、解题技巧,也可先求出127+(-9)=118,再变成补码后去与可供选择的答案对比。

13.浮点数加、减运算过程一般包括对阶、尾数运算、规格化、舍入和判溢出等步骤。设浮点数的阶码和尾数均采用补码表示,且位数分别为5位和7位(均含2位符号位)。若有两个数X = 2729/32,Y = 255/8,则用浮点加法计算X+Y的最终结果是

A.00111 1100010 B.00111 0100010

C.01000 0010001 D.发生溢出

[答案] D

[解析] 1、十进制小数到二进制的转换,小数与整数的补码表示;

2、浮点数的阶码(整数)、尾数(尾数)的表示,规格化的概念;

3、浮点数的加法运算与结果溢出检查;

[X]浮=00111 0011101,[Y]浮=00101 0010100=00111 0000101

X和Y的尾数相加的0100010,应规格化,成为0010001,阶码要加1,将变成8,但阶码的数值位用3位补码表示,不能表示正8,表明运算结果是溢出了。

4、解题技巧

A) 也可先把25×5/8变成27×5/8/4=27×5/32,再计算29/32+5/32=34/32=2×17/32, 表明需要阶码加1,将变成8,已经不能表示,是溢出。

B) 千万不要变分数为小数之后再转换成二进制,分母是2的整数幂时只需转换其分子部分,这对于解这个题实在是太重要了。

14.某计算机的Cache共有16块,采用2路组相联映射方式(即每组2块)。每个主存块大小为32字节,按字节编址。主存129号单元所在主存块应装入到的Cache组号是

A.0 B.2 C.4 D.6

[答案] C

[解析] 1、Cache与主存之间的地址映射关系;

2、三种Cache的组织方式(其实本题未测试这一点,是直接映射还是两路组相联与答案不相关);129 MOD 32 = 4 余1,所以答案为C,注意Cache的组号从0开始编码。

3、注:本题设映射关系为:i=j mod v (其中i为cache 的组号,j为主存的块号),m=v×k(m为cache中的块数,v为cache中的组数,k为每组包含的块数)。则答案为C。

假如设映射关系为:i=[j/2^t]mod 2^g , (其中i为cache 的组号, j为主存的块号, 2^t为组内的块数,2^g为cache分的组数 )。则答案为B。

15.某计算机主存容量为64 KB,其中ROM区为4 KB,其余为RAM区,按字节编址。现要用2 K×8位的ROM芯片和4 K×4位的RAM芯片来设计该存储器,则需要上述规格的ROM芯片数和RAM芯片数分别是

A.1、15 B.2、15 C.1、30 D.2、30

[答案] D

[解析] 1、一个字节Byte由8个二进制位bit组成;

2、存储器的字位扩展技术,选用已有芯片构建存储器;

计算: 4KB的ROM要用2K×8位的器件2片;60KB的RAM要用4K×4位的芯片数量是(60K×8)/(4K×4)=30;

16.某机器字长16位,主存按字节编址,转移指令采用相对寻址,由两个字节组成,第一字节为操作码字段,第二字节为相对位移量字段。假定取指令时,每取一个字节PC自动加1。若某转移指令所在主存地址为2000H,相对位移量字段的内容为06H,则该转移指令成功转移后的目标地址是

A.2006H B.2007H C.2008H D.2009H

[答案] C

[解析] 1、指令的寻址方式,相对寻址的执行过程

2、指令的执行步骤与每一步的操作功能;

计算机按字节寻址,相对转移指令在2000H单元,则取出这条指令后PC的值应为2002H,因为取指的同时将执行PC增量操作(此处增量值为2,而不是1),相对位移量的值是6,故转移目标地址应为2008H。

17.下列关于RISC的叙述中,错误的是

A.RISC普遍采用微程序控制器

B.RISC大多数指令在一个时钟周期内完成

C.RISC的内部通用寄存器数量相对CISC多

D.RISC的指令数、寻址方式和指令格式种类相对CISC少

[答案] A

[解析] 1、相对于CISC计算机,RISC计算机的特点表现在哪些方面;

2、组合逻辑控制器和微程序控制器的组成与性能的同异之处;

18.某计算机的指令流水线由四个功能段组成,指令流经各功能段的时间(忽略各功能段之间的缓存时间)分别为90 ns、80 ns、70 ns和60 ns,则该计算机的CPU时钟周期至少是

A.90 ns B.80 ns C.70 ns D.60 ns

[答案] A

[解析] 1、如何确定每个流水步的时间长度,时钟周期应以最长的执行时间为准,否则用时

长的流水段的功能将不能正确完成。

19.相对于微程序控制器,硬布线控制器的特点是

A.指令执行速度慢,指令功能的修改和扩展容易

B.指令执行速度慢,指令功能的修改和扩展难

C.指令执行速度快,指令功能的修改和扩展容易

D.指令执行速度快,指令功能的修改和扩展难

[答案] D

[解析] 1、组合逻辑控制器和微程序控制器的组成与性能的同异之处。

20.假设某系统总线在一个总线周期中并行传输4字节信息,一个总线周期占用2个时钟周期,总线时钟频率为10 MHz,则总线带宽是

A.10 MB/s B.20 MB/s C.40 MB/s D.80 MB/s

[答案] B。

[解析] 1、总线的带宽等于总线周期的频率×每个总线周期传送的信息数量。

按题意,(10×106 /2)×4 = 20×106 (MB/s)。

21.假设某计算机的存储系统由Cache和主存组成。某程序执行过程中访存1000次,其中访问Cache缺失(未命中)50次,则Cache的命中率是

A.5% B.9.5% C.50% D.95%

[答案] D

[解析] 1、Cache与主存之间的地址映射关系。

2、三种Cache的组织方式(其实本题未测试这一点,是直接映射还是两路组相联与答案不相关);

3、Cache的命中率。计算:命中率为 (1000-50) / 1000 = 95%

22.下列选项中,能引起外部中断的事件是

A.键盘输入 B.除数为0 C.浮点运算下溢 D.访存缺页

[答案] A

[解析] 1、中断的分类。

能引起外部中断的只能是输入设备键盘。

二. 综合应用题

43.(8分)某计算机的CPU主频为500 MHz,CPI为5(即执行每条指令平均需5个时钟周期)。假定某外设的数据传输率为0.5 MB/s,采用中断方式与主机进行数据传送,以32位为传输单位,对应的中断服务程序包含18条指令,中断服务的其他开销相当于2条指令的执行时间。请回答下列问题,要求给出计算过程。

(1) 在中断方式下,CPU用于该外设I/O的时间占整个CPU时间的百分比是多少?

(2)当该外设的数据传输率达到5 MB/s时,改用DMA方式传送数据。假定每次DMA传送块大小为5000 B,且DMA预处理和后处理的总开销为500个时钟周期,则CPU用于该外设I/O的时间占整个CPU时间的百分比是多少?(假设DMA与CPU之间没有访存冲突)

[答案]

(1)中断方式下,CPU每次用于数据传送的时钟周期数:518 +52 = 100

为达到外设0.5 MB/s的数据传输率,外设每秒申请的中断次数:

0.5 MB /4 B = 125 000

1秒钟内用于中断的开销:

100 125 000 = 12500 000 = 12.5 M个时钟周期

CPU用于外设I/O的时间占整个CPU时间的百分比:12.5 M/500 M = 2.5%

(2)外设数据传输率提高到5 MB/s时,1秒钟内需产生的DMA次数:

5 MB/5 000 B = 1000

CPU用于DMA处理的总开销:1000 500 = 500 000 = 0.5 M个时钟周期

CPU用于外设I/O的时间占整个CPU时间的百分比:

0.5 M /500 M = 0.1%

[解析] 在答案中已加入分析。

44.(13分)某计算机字长16位,采用16位定长指令字结构,部分数据通路结构如下图所示(见下页),图中所有控制信号为1时表示有效、为0时表示无效,例如控制信号MDRinE为1表示允许数据从DB打入MDR,MDRin为1表示允许数据从内总线打入MDR。假设MAR的输出一直处于使能状态。加法指令“ADD (R1),R0”的功能为(R0)+((R1))(R1),即将R0中的数据与R1的内容所指主存单元的数据相加,并将结果送入R1的内容所指主存单元中保存。

下表给出了上述指令取指和译码阶段每个节拍(时钟周期)的功能和有效控制信号,请按表中描述方式用表格列出指令执行阶段每个节拍的功能和有效控制信号。

时钟 功能 有效控制信号

C1 MAR←(PC) PCout,MARin

C2 MDR←M(MAR)

PC←(PC)+1 MemR,MDRinE

PC+1

C3 IR←(MDR) MDRout,IRin

C4 指令译码 无

[答案] 参考答案一:

时钟 功能 有效控制信号

C5 MAR←(R1) R1out,MARin

C6 MDR←M(MAR)

A←(R0) MemR,MDRinE

R0out,Ain

C7 AC←(MDR)+(A) MDRout,Add,ACin

C8 MDR←(AC) ACout,MDRin

C9 M(MAR)←(MDR) MDRoutE,MemW

“A←(R0)”也可在C7:“AC←(MDR)+(A)”之前单列的一个时钟周期内执行。

参考答案二:

时钟 功能 有效控制信号

C5 MAR←(R1) R1out,MARin

C6 MDR←M(MAR) MemR,MDRinE

C7 A←(MDR) MDRout,Ain

C8 AC←(A)+ (R0) R0out,Add,ACin

C9 MDR←(AC) ACout,MDRin

C10 M(MAR)←(MDR) MDRoutE,MemW

[解析]

一条指令的执行过程通常由取指、译码和执行3个步骤完成,本题中取指用3个节拍、译码用1个节拍,执行加法运算并把结果写入主存如何完成呢?包括划分执行步骤、确定完成的功能、要提供的控制信号,这是本题的要测试的内容。为回答这个问题,首先需要看清图中给出的部件组成情况和信息传送的路径。

要完成的功能是 (R0) + ((R1))→(R1),从图中看到:

(1) R0、R1都有送自己内容到内总线的路径,控制信号分别是R0in和R1in;

(2) ALU加运算,2个数据由工作寄存器A和内总线提供,控制信号是Add;累加器AC只接收内总线的内容,控制信号是Ain;结果需存AC,控制信号是ACin;AC的内容可送内总线,控制信号是ACout;

(3) PC可接收内总线的内容,还可增1,控制信号是PCin和PC+1,PC的内容可送内总线,控制信号是PCout;

(4) 指令寄存器IR可接收内总线的内容,控制信号是IRin;

(5) 读写存储器时,地址由MAR经AB提供,MAR只接收内总线上的信息,控制信号是MARin;

(6) 读存储器,提供读命令MemR,并通过DB送入MDR,控制信号是MDRinE;MDR的内容可送内总线,控制信号是MDRout;

(7)写存储器,提供写命令MemW,数据由MDR通过DB送到存储器的数据引脚,控制信号是MDRoutE;

然后是划分执行步骤、确定每一步完成的功能、需要提供的控制信号。这是由指令应完成的功能和计算机硬件的实际组成情况和信息传送的可用路径共同决定的。基本原则是步骤越少越好,硬件电路要能支持,可以有多种方案,解题时应参照已给出的答题格式,即取指和译码执行过程的那张表的内容,但不必把表已有的内容再抄一遍。

划分指令执行步骤,确定每一步完成的功能、给出需要提供的控制信号:

请注意,(R0)+((R1))表示:R0寄存器的内容与R1作地址从主存中读出来的数据完成加法运算;而 →(R1)表示把R1的内容作为主存储器的地址完成写主存操作。为防止出现误解,题中还特地对此作了文字说明。这条指令的功能是先到主存储器取一个数,之后运算,再将结果写回主存储器。

(1) 执行相加运算,需把存储器中的数据读出,为此首先送地址,即R1的内容送MAR,控制信号是R1out,MARin。

(2) 启动读主存操作,读出的内容送入MDR,控制信号是MemR,MDRinE,

还可同时把R0的内容经内总线送入A,用到的控制信号是R0out,Ain。

(3) 执行加法运算,即A的内容与MDR的内容相加,结果保存到AC,

控制信号是MDRout,Add,ACin。

(4) 要把AC的内容写入主存,由于R1的内容已经在MAR中,地址已经有了,但需要把写入的数据(已经在AC)中)经内总线送入MDR;

控制信号是ACout, MDRin。

(5) 给出写主存的命令,把MDR的内容经DB送存储器的数据线引脚,执行写操作,控制信号是MDRoutE, MemW。

这几个步骤是有先后次序的,前面的完成了,下一步才可以执行,也保证了不会产生硬件线路的冲突。请注意,使用最为频繁的是内总线,它在任何时刻只能接收一个输入数据,并且向内总线发送信息的电路只能以三态门器件连接到内总线,5个向内总线发送信息的控制信号(ACout,PCout,R0out,R1out,MDRout)最多只能有一个为1,其它4个必须全为0,或者5个全为0。

仔细看一下,发现可以把第2个步骤的操作划分到两个步骤中完成,一个步骤中安排MDR接收从存储器中读出的内容,到另外一个步骤实现R0的内容送入A,这多用了一个操作步骤,指令的执行速度会变慢。有些解题者在写存储器之前,还会再执行一次把R1的内容送MAR,尽管无此必要,但不属于原理上的错误。

当然还可以有其它的设计结果。

解题时这些叙述内容不必写出来(我们写出这些内容是希望帮助大家领会本题要测试的知识点和指令的执行过程),直接按照已经给出的表格的形式、按照提供的填写办法把设计的表格及其内容填写好就可以了。

以上就是关于“2024考研计算机组成原理试题汇总(5)”的内容,更多计算机研究生真题精彩内容,请持续关注新东方在线考研频道!

【计算机】资料这里有↑↑↑

资料下载

资料下载

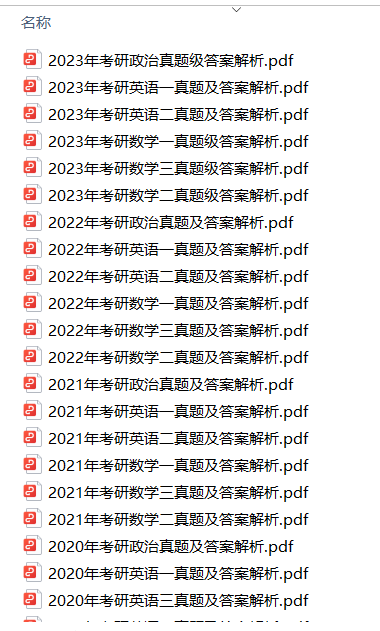

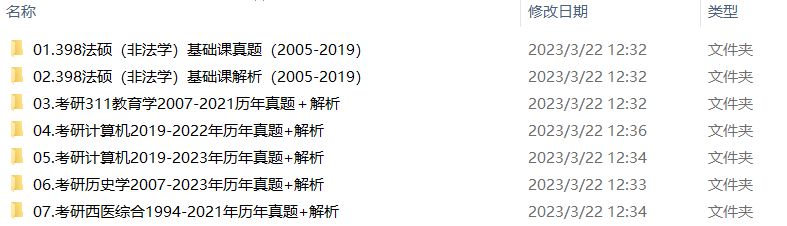

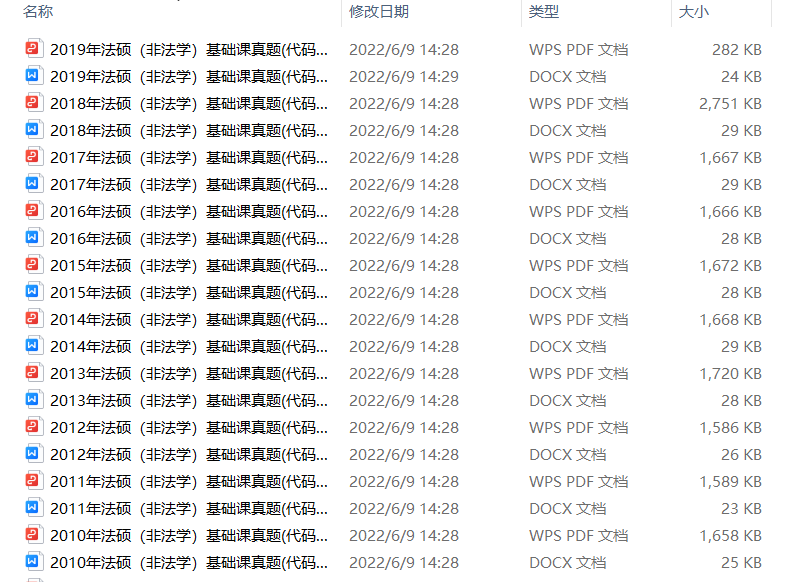

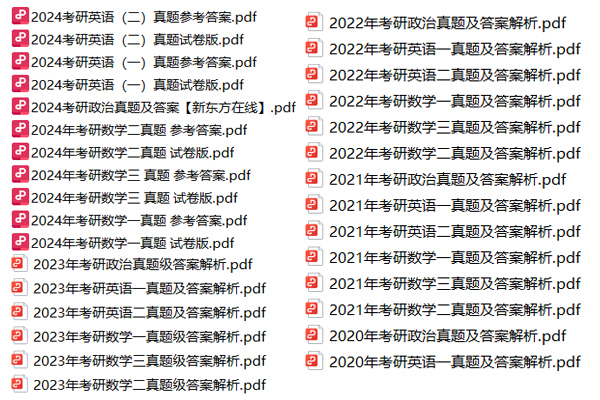

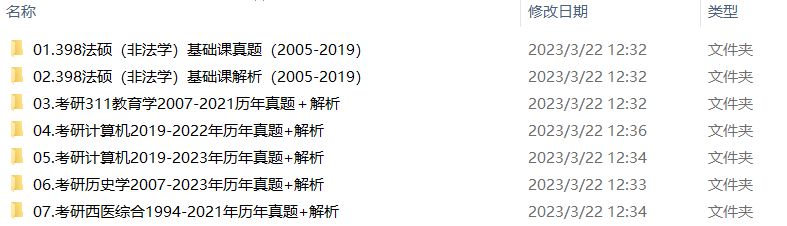

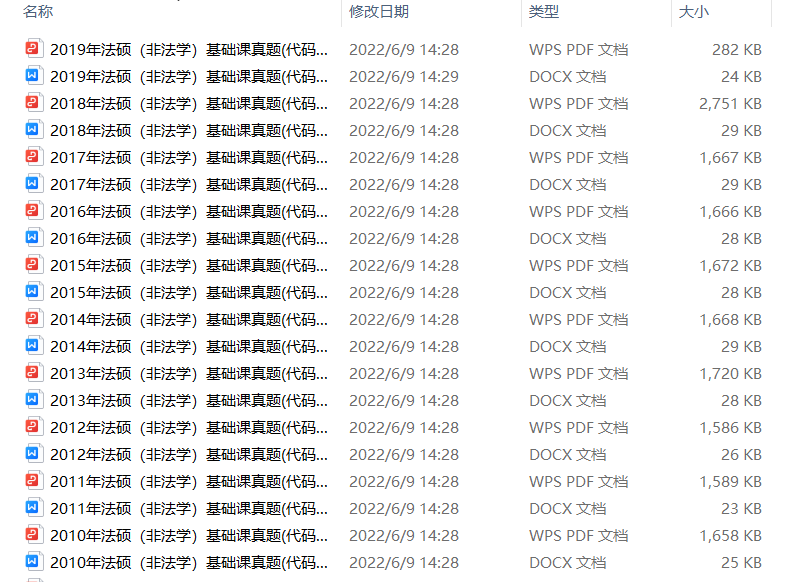

2014年-2025年考研历年真题汇总

发布时间:2024-04-25扫码添加【考研班主任】

即可领取资料包

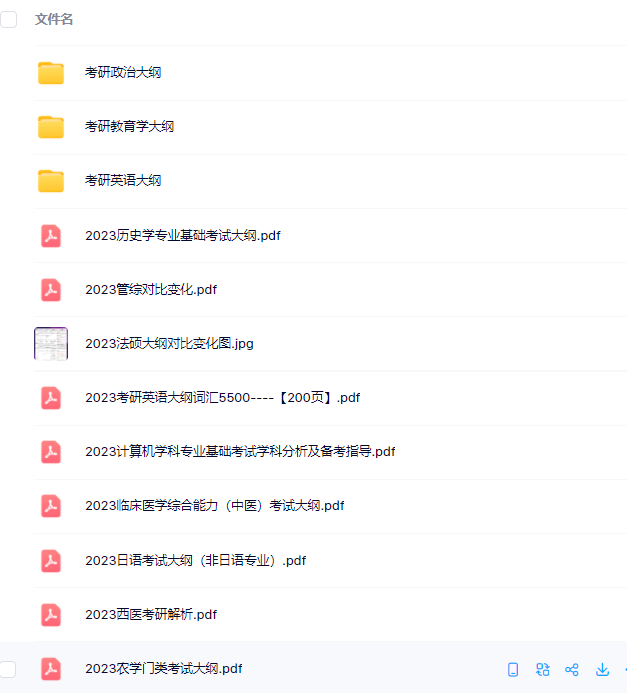

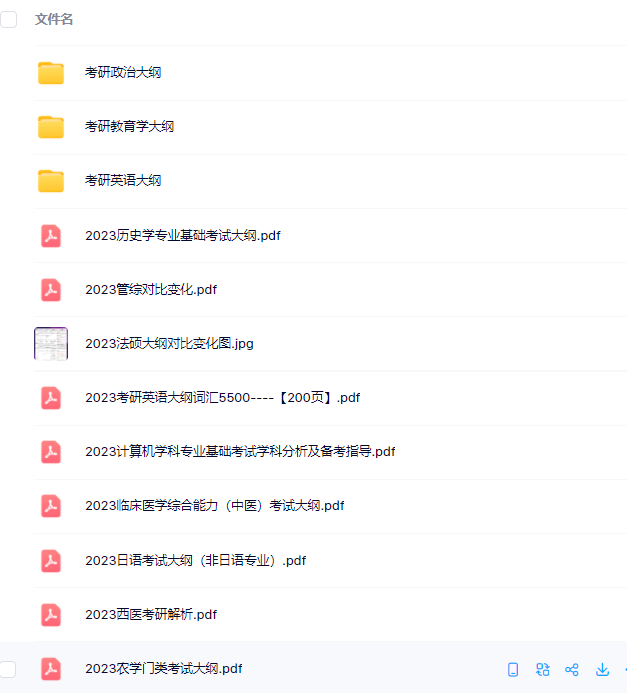

考研大纲PDF电子版下载-历年(附解析)

发布时间:2024-04-25扫码添加【考研班主任】

即可领取资料包

2026年考研政数英备考资料zip压缩包

发布时间:2024-04-25扫码添加【考研班主任】

即可领取资料包

考研英语大纲词汇5500打印版(基础必备)

发布时间:2024-04-25扫码添加【考研班主任】

即可领取资料包

新东方在线考试模拟题【12套】

发布时间:2024-04-25扫码添加【考研班主任】

即可领取资料包

2026年考研专业课知识点总结

发布时间:2024-04-25扫码添加【考研班主任】

即可领取资料包

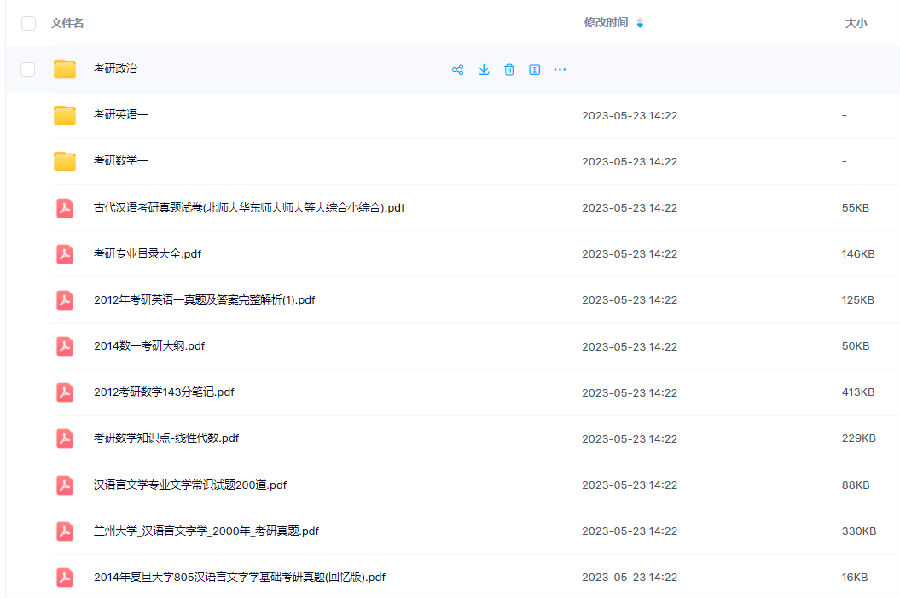

新东方考研资料下载地址

发布时间:2023-05-17新东方在线考研资料合集

下载方式:微信扫码,获取网盘链接

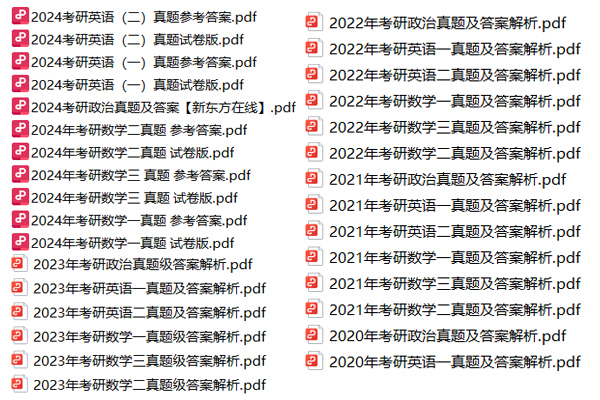

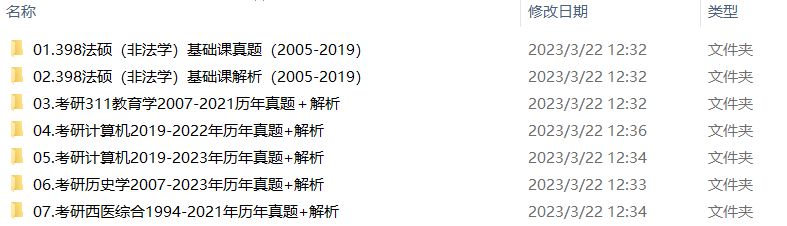

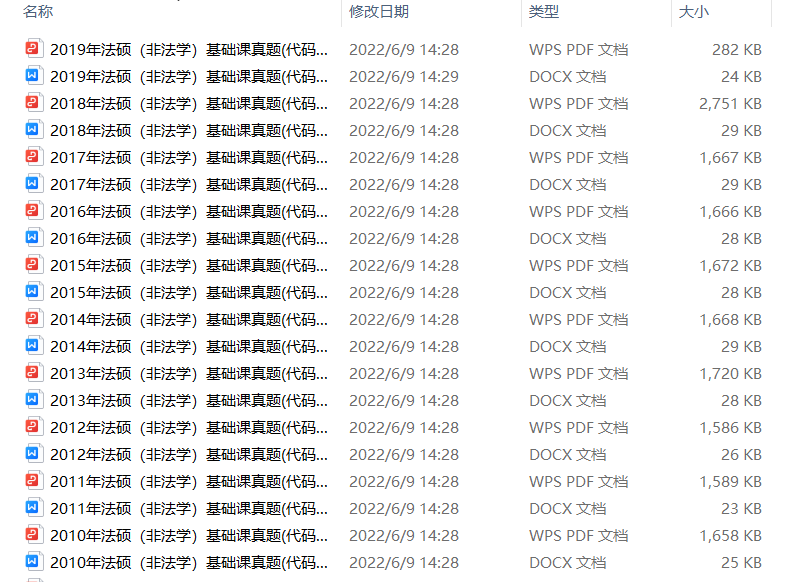

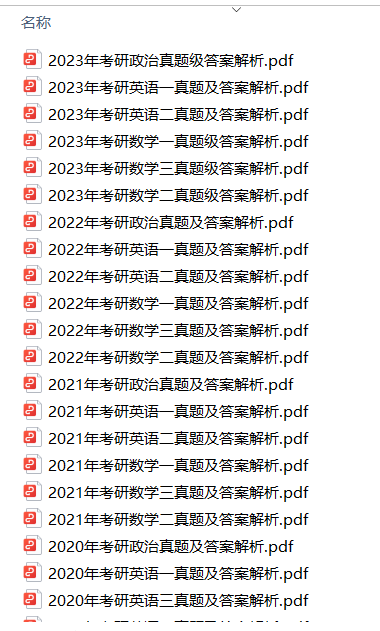

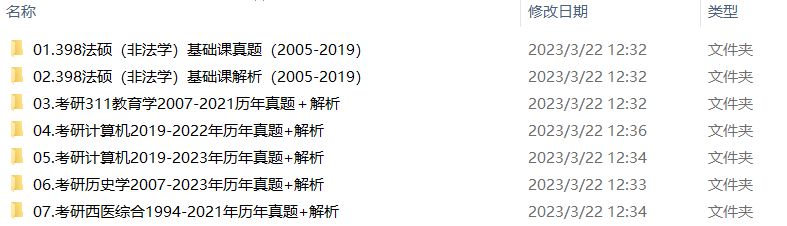

目录:

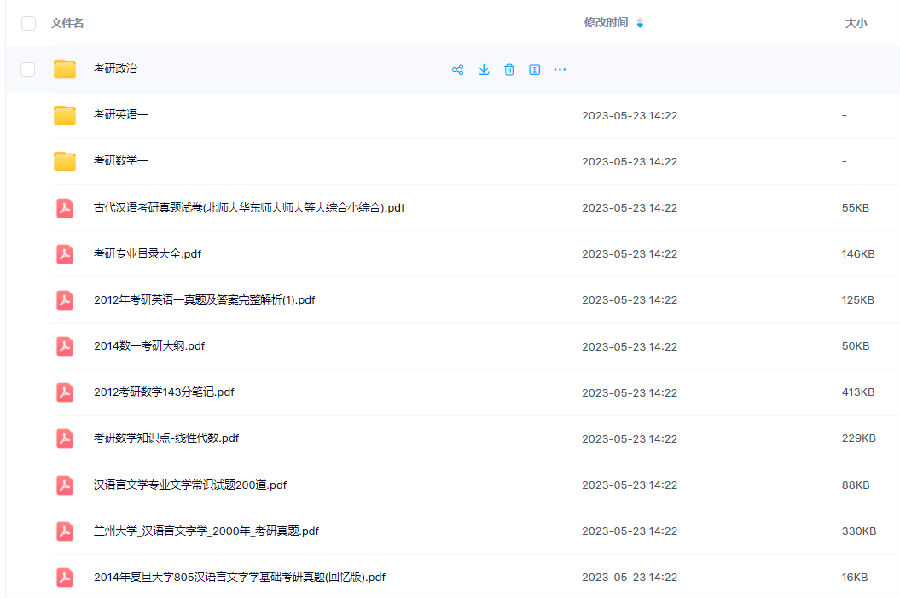

1.2013-2023年近10年政数英真题及解析PDF版(新东方)

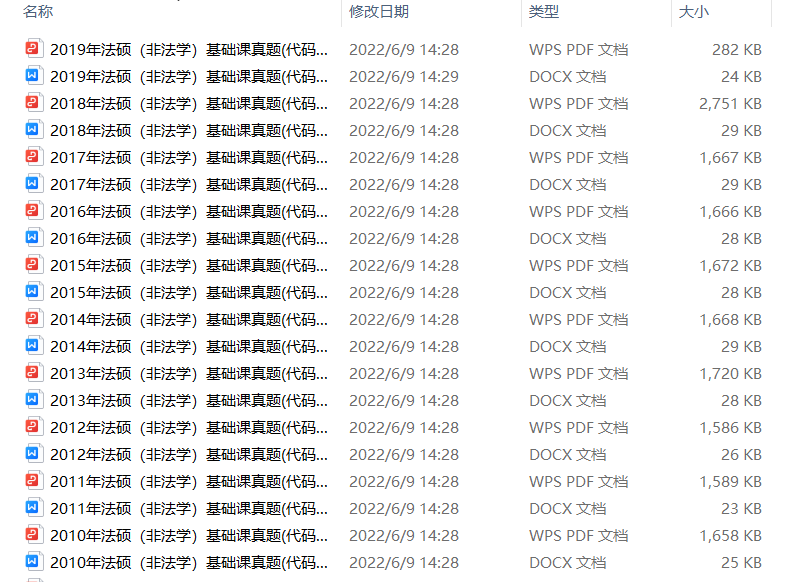

2.2013-2023年专业课考试历年真题及解析PDF版

3.24考研复习备考资料大合集:大纲+备考资料+词汇书+考前押题+自命题

资料介绍:

1.2013-2023年近10年政数英真题及解析PDF版(新东方)

、

、

2.2013-2023年专业课考试历年真题及解析PDF版

3.24考研复习备考资料大合集

3.24考研复习备考资料:考研大纲

3.24考研复习备考资料:政数英备考资料+自命题真题

------------------

考研备考过程中,尤其是专业课部分,参考往年的考试真题,对于我们的复习有更好的帮助。北京大学考研真题资料都有哪些?小编为大家进行了汇总。

北京大学考研真题资料-公共课

北京大学考研真题资料-专业课

以上就是关于“北京大学考研真题资料下载(历年汇总)”的整理,更多考研资料下载,请关注微信获取下载地址。

2024考研公共课必背知识点汇总

发布时间:2023-01-03扫码添加【考研班主任】

即可领取资料包

2013-2023考研历年真题汇总

发布时间:2023-01-03扫码添加【考研班主任】

即可领取资料包

考研英语大纲词汇(PDF可打印)

发布时间:2023-01-03扫码添加【考研班主任】

即可领取资料包

2024考研专业课知识点总结

发布时间:2023-01-03扫码添加【考研班主任】

即可领取资料包

2023考研政治 内部押题 PDF

发布时间:2022-11-16扫码添加【考研班主任】

即可领取资料包

徐涛:23考研预测六套卷

发布时间:2022-11-16扫码添加【考研班主任】

即可领取资料包

考研政数英冲刺资料最新整理

发布时间:2022-11-16扫码添加【考研班主任】

即可领取资料包

23考研答题卡模板打印版

发布时间:2022-11-16扫码添加【考研班主任】

即可领取资料包

2023考研大纲词汇5500PDF电子版

发布时间:2022-07-28扫码添加【考研班主任】

即可领取资料包

考研历年真题(公共课+专业课)

发布时间:2022-07-28扫码添加【考研班主任】

即可领取资料包

考研英语阅读100篇附解析及答案

发布时间:2022-01-07扫码添加【考研班主任】

即可领取资料包

新东方考研学霸笔记整理(打印版)

发布时间:2022-01-07扫码添加【考研班主任】

即可领取资料包

2001-2021年考研英语真题答案(可打印版)

发布时间:2022-01-07扫码添加【考研班主任】

即可领取资料包

考研英语词汇5500(完整版下载)

发布时间:2022-01-07扫码添加【考研班主任】

即可领取资料包

2022考研政审表模板精选10套

发布时间:2022-01-07扫码添加【考研班主任】

即可领取资料包

历年考研真题及答案 下载

发布时间:2021-12-09扫码添加【考研班主任】

即可领取资料包

考研政审表模板汇总

发布时间:2020-06-17扫码添加【考研班主任】

即可领取资料包

近5年考研英语真题汇总

发布时间:2020-06-17扫码添加【考研班主任】

即可领取资料包

考研英语大纲词汇5500

发布时间:2020-06-17扫码添加【考研班主任】

即可领取资料包

2022考研12大学科专业排名汇总

发布时间:2019-11-21扫码添加【考研班主任】

即可领取资料包

2023考研政治复习备考资料【珍藏版】

发布时间:2019-11-21扫码添加【考研班主任】

即可领取资料包

考研英语万能模板+必备词汇+范文

发布时间:2019-11-21扫码添加【考研班主任】

即可领取资料包

考研数学一、二、三历年真题整理

发布时间:2019-11-21扫码添加【考研班主任】

即可领取资料包

添加班主任领资料

添加考研班主任

免费领取考研历年真题等复习干货资料

推荐阅读

推荐阅读

2025年考研初试结束后,新东方在线为大家整理了:2025考研计算机专业基础综合真题答案:综合应用题,供大家参考,同时也为大家提供了电

2025年考研初试结束后,新东方在线为大家整理了:2025考研计算机专业基础综合真题答案:单选题,供大家参考,同时也为大家提供了电子版

2025年考研初试结束后,新东方在线为大家整理了:2025考研计算机专业基础综合真题答案:计算机网络,供大家参考,同时也为大家提供了电

2025年考研初试结束后,新东方在线为大家整理了:2025考研计算机专业基础综合真题答案:操作系统,供大家参考,同时也为大家提供了电子

2025年考研初试结束后,新东方在线为大家整理了:2025考研计算机专业基础综合真题答案:计算机组成原理,供大家参考,同时也为大家提供

资料下载

资料下载

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

新东方在线考研资料合集

下载方式:微信扫码,获取网盘链接

目录:

1.2013-2023年近10年政数英真题及解析PDF版(新东方)

2.2013-2023年专业课考试历年真题及解析PDF版

3.24考研复习备考资料大合集:大纲+备考资料+词汇书+考前押题+自命题

资料介绍:

1.2013-2023年近10年政数英真题及解析PDF版(新东方)

、

、

2.2013-2023年专业课考试历年真题及解析PDF版

3.24考研复习备考资料大合集

3.24考研复习备考资料:考研大纲

3.24考研复习备考资料:政数英备考资料+自命题真题

------------------

考研备考过程中,尤其是专业课部分,参考往年的考试真题,对于我们的复习有更好的帮助。北京大学考研真题资料都有哪些?小编为大家进行了汇总。

北京大学考研真题资料-公共课

北京大学考研真题资料-专业课

以上就是关于“北京大学考研真题资料下载(历年汇总)”的整理,更多考研资料下载,请关注微信获取下载地址。

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

阅读排行榜

阅读排行榜

相关内容

相关内容