特惠-26考研冲刺

特惠-27考研课

双证-在职硕士

免联考-同等学力

复试分数线

26复试全面指导

模拟复试面试

26考研-全套真题

26考研估分

保研-路线图

27考研-智能择校

27考研-英语测评

27考研-新大纲对比

热门-计算机择校

扫码加入训练营

牢记核心词

学习得礼盒

目前各大院校开始陆续公布2023考研复试大纲的相关内容,对于同学们来说,我们还是需要及时关注院校发布的大纲内容,这样可以帮助我们圈定复试复习内容,做好相应的备考。下面小编为大家整理了“哈尔滨理工大学2023考研复试考试大纲:硬件描述语言”,供大家参考。

哈尔滨理工大学2023考研复试考试大纲:硬件描述语言

硬件描述语言

一、试卷满分及考试时间

试卷满分为 100 分,考试时间为 120 分钟。

二、答题方式

答题方式为闭卷、笔试。

三、试卷内容结构

1. Verilog的基本语法和语句

2. 设计流程、不同层次建模的应用场合、验证、综合的概念及意义

3. 采用适当语句对电路进行门级、数据流级、行为级建模并验证

四、试卷题型结构

1. 填空题 10 空,每空 2 分,共 20 分

2. 简述题 4 小题,每题 5 分,共 20 分

3. 编程题 5 小题,共 60 分.

考试内容:

一、设计方法学

1. 自顶向下(Top_Down)设计的基本概念

2. 采用硬件描述语言的设计流程

二、Verilog HDL基本语法

1. Verilog HDL语法要素,包括标识符、格式、编译指令、数值表示、数据类型、参数定义等

2. Verilog HDL表达式构成,包括操作符、操作数、表达式构成等

三、Verilog HDL门级建模

1. Verilog HDL门级原语使用

2. 使用可综合原语对电路进行门级建模

四、Verilog的层次化建模方法

1. 层次化建模方法,层次化命名

2. 实例化语句,顺序端口连接、命名端口连接

五、Verilog HDL数据流建模

1. 连续性赋值语句(assign)

2. 使用assign语句对组合逻辑电路建模

六、Verilog HDL行为级建模

1. 行为级描述语句,包括过程语句、时序控制、块语句、任务和函数、阻塞与非阻塞、条件分支语句。

2. 使用Verilog HDL对并行加法器、乘法器、计数器等简单组合逻辑电路进行行为级建模

七、验证

1.采用激励、响应的验证方法。

2.编写testbench对待测设计进行验证。

八、综合

1.综合的概念及意义

2.可综合编码风格

考试要求:

1. 掌握采用Verilog HDL的设计流程

2. 掌握Verilog基本语法

3. 掌握门级建模方法

4. 掌握层次化命名及实例化方法

5. 掌握使用assign语句进行电路建模

6. 掌握使用行为语句进行电路建模

7. 掌握使用测试平台对待测设计进行验证

8. 掌握综合的基本概念及电路在不同设计阶段的表现形式

9. 掌握可综合编码风格

以上就是关于“哈尔滨理工大学2023考研复试考试大纲:硬件描述语言”的介绍,希望帮助大家更好的来复习备考。

资料下载

资料下载

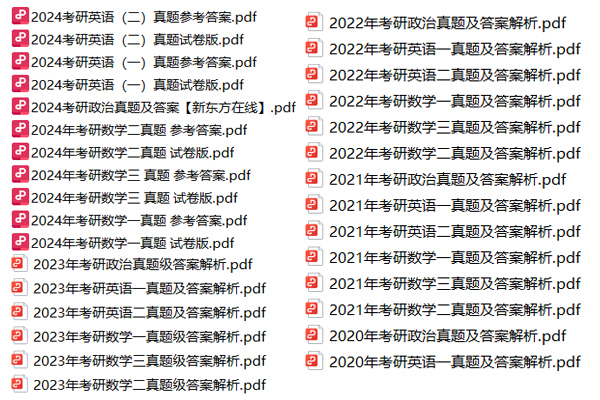

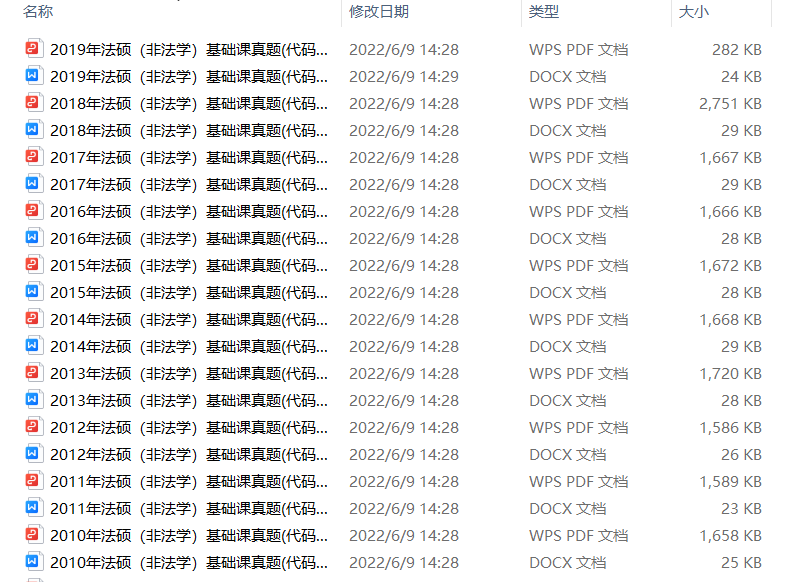

2014年-2025年考研历年真题汇总

发布时间:2024-04-25扫码添加【考研班主任】

即可领取资料包

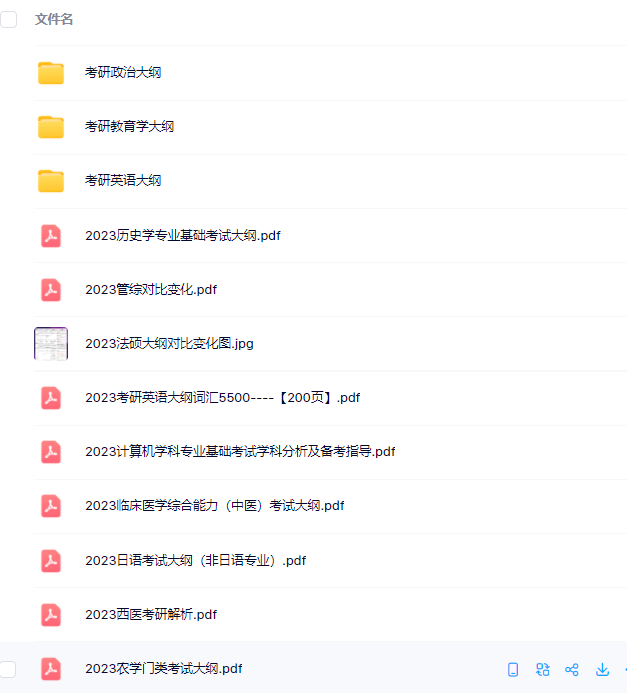

考研大纲PDF电子版下载-历年(附解析)

发布时间:2024-04-25扫码添加【考研班主任】

即可领取资料包

2026年考研政数英备考资料zip压缩包

发布时间:2024-04-25扫码添加【考研班主任】

即可领取资料包

考研英语大纲词汇5500打印版(基础必备)

发布时间:2024-04-25扫码添加【考研班主任】

即可领取资料包

新东方在线考试模拟题【12套】

发布时间:2024-04-25扫码添加【考研班主任】

即可领取资料包

2026年考研专业课知识点总结

发布时间:2024-04-25扫码添加【考研班主任】

即可领取资料包

新东方考研资料下载地址

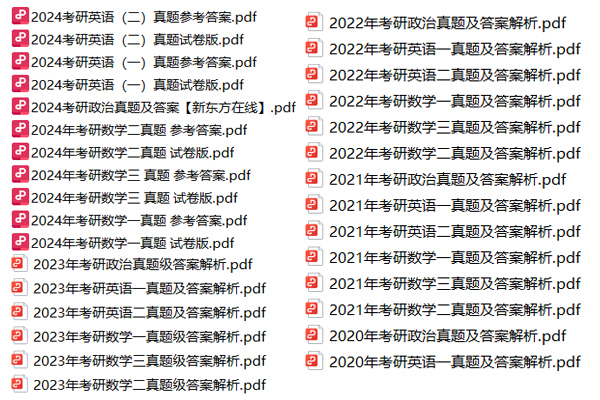

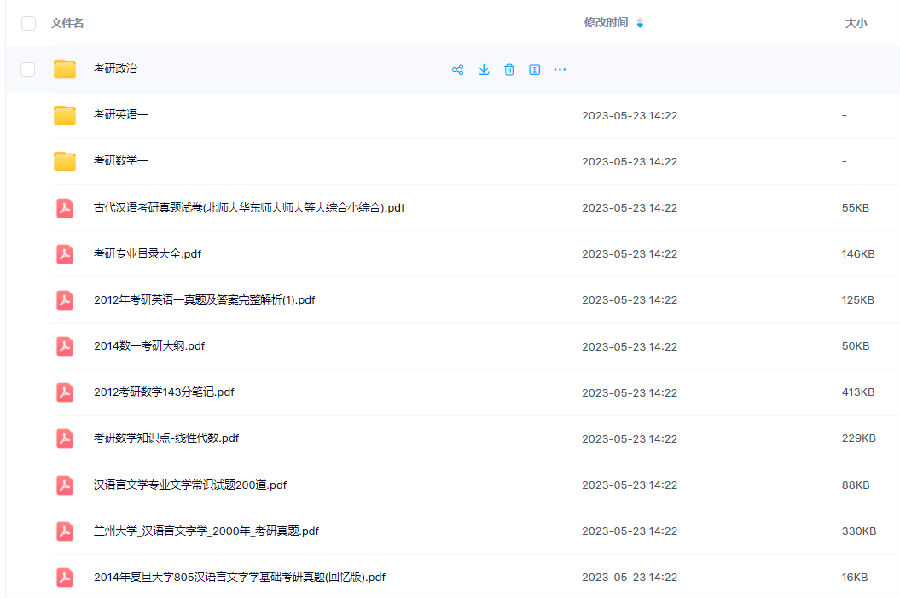

发布时间:2023-05-17新东方在线考研资料合集

下载方式:微信扫码,获取网盘链接

目录:

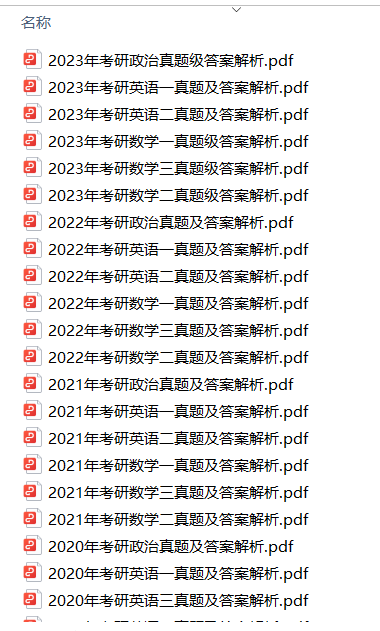

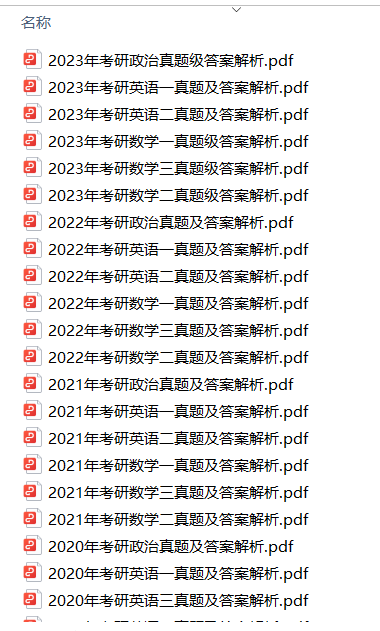

1.2013-2023年近10年政数英真题及解析PDF版(新东方)

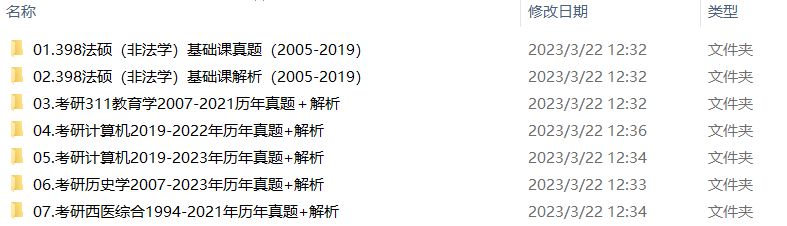

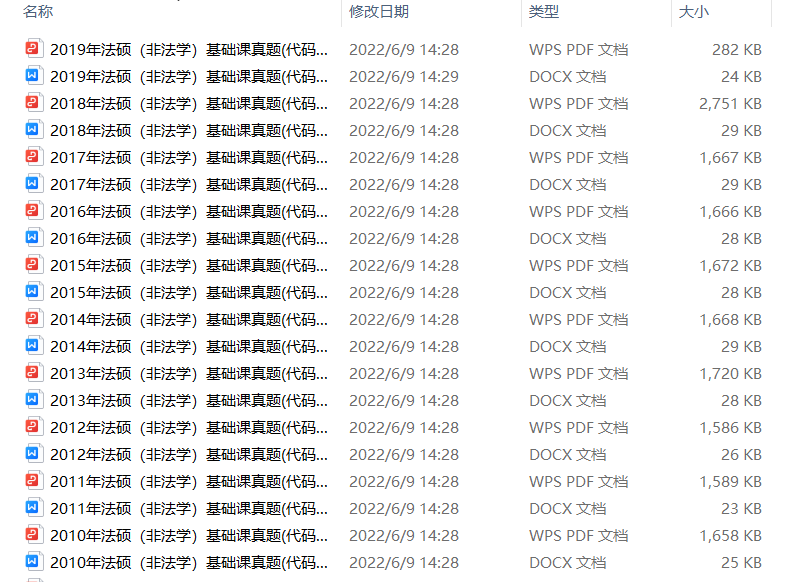

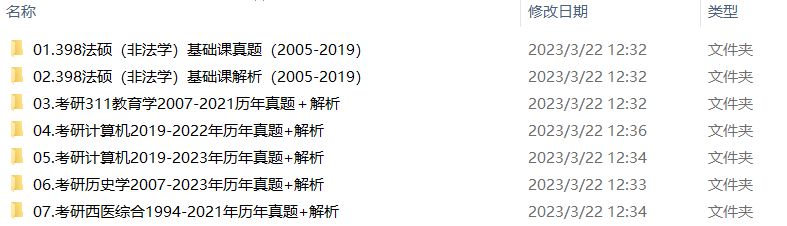

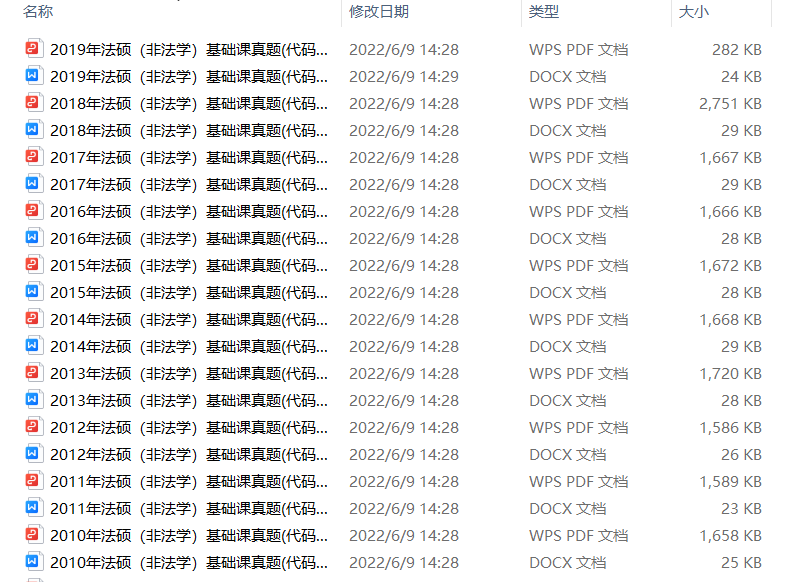

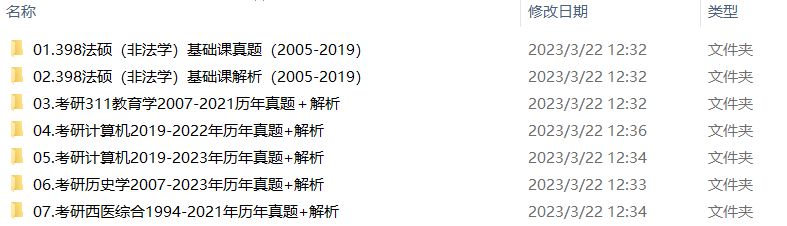

2.2013-2023年专业课考试历年真题及解析PDF版

3.24考研复习备考资料大合集:大纲+备考资料+词汇书+考前押题+自命题

资料介绍:

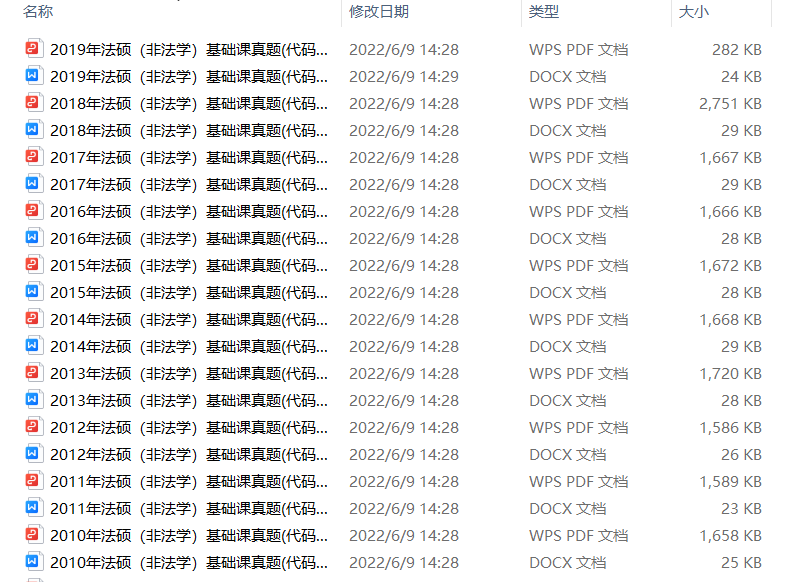

1.2013-2023年近10年政数英真题及解析PDF版(新东方)

、

、

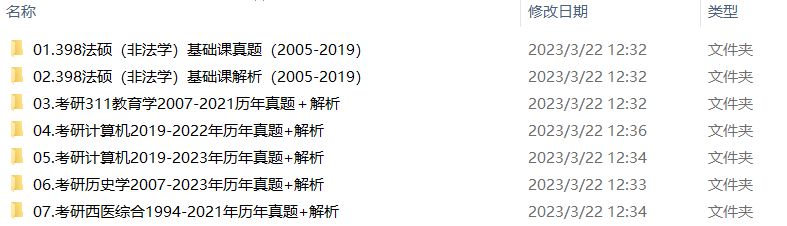

2.2013-2023年专业课考试历年真题及解析PDF版

3.24考研复习备考资料大合集

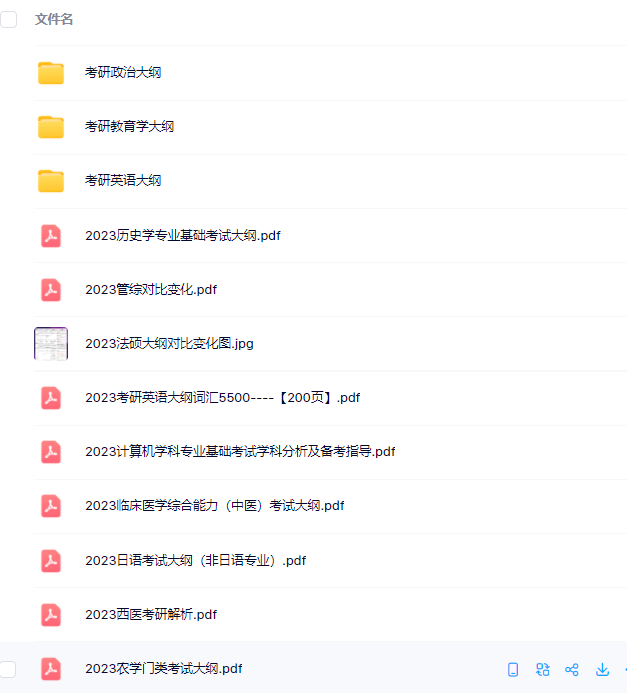

3.24考研复习备考资料:考研大纲

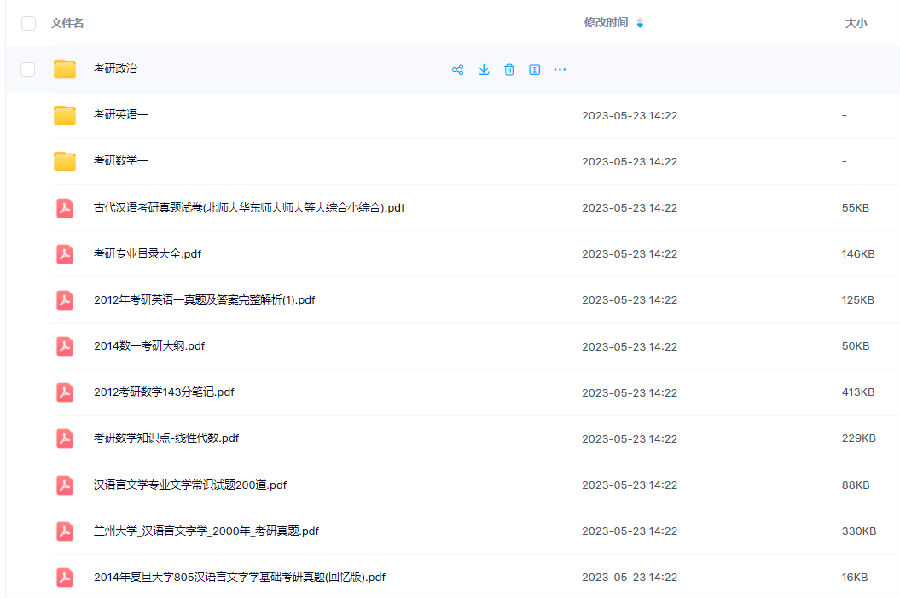

3.24考研复习备考资料:政数英备考资料+自命题真题

------------------

考研备考过程中,尤其是专业课部分,参考往年的考试真题,对于我们的复习有更好的帮助。北京大学考研真题资料都有哪些?小编为大家进行了汇总。

北京大学考研真题资料-公共课

北京大学考研真题资料-专业课

以上就是关于“北京大学考研真题资料下载(历年汇总)”的整理,更多考研资料下载,请关注微信获取下载地址。

2024考研公共课必背知识点汇总

发布时间:2023-01-03扫码添加【考研班主任】

即可领取资料包

2013-2023考研历年真题汇总

发布时间:2023-01-03扫码添加【考研班主任】

即可领取资料包

考研英语大纲词汇(PDF可打印)

发布时间:2023-01-03扫码添加【考研班主任】

即可领取资料包

2024考研专业课知识点总结

发布时间:2023-01-03扫码添加【考研班主任】

即可领取资料包

2023考研政治 内部押题 PDF

发布时间:2022-11-16扫码添加【考研班主任】

即可领取资料包

徐涛:23考研预测六套卷

发布时间:2022-11-16扫码添加【考研班主任】

即可领取资料包

考研政数英冲刺资料最新整理

发布时间:2022-11-16扫码添加【考研班主任】

即可领取资料包

23考研答题卡模板打印版

发布时间:2022-11-16扫码添加【考研班主任】

即可领取资料包

2023考研大纲词汇5500PDF电子版

发布时间:2022-07-28扫码添加【考研班主任】

即可领取资料包

考研历年真题(公共课+专业课)

发布时间:2022-07-28扫码添加【考研班主任】

即可领取资料包

考研英语阅读100篇附解析及答案

发布时间:2022-01-07扫码添加【考研班主任】

即可领取资料包

新东方考研学霸笔记整理(打印版)

发布时间:2022-01-07扫码添加【考研班主任】

即可领取资料包

2001-2021年考研英语真题答案(可打印版)

发布时间:2022-01-07扫码添加【考研班主任】

即可领取资料包

考研英语词汇5500(完整版下载)

发布时间:2022-01-07扫码添加【考研班主任】

即可领取资料包

2022考研政审表模板精选10套

发布时间:2022-01-07扫码添加【考研班主任】

即可领取资料包

历年考研真题及答案 下载

发布时间:2021-12-09扫码添加【考研班主任】

即可领取资料包

考研政审表模板汇总

发布时间:2020-06-17扫码添加【考研班主任】

即可领取资料包

近5年考研英语真题汇总

发布时间:2020-06-17扫码添加【考研班主任】

即可领取资料包

考研英语大纲词汇5500

发布时间:2020-06-17扫码添加【考研班主任】

即可领取资料包

2022考研12大学科专业排名汇总

发布时间:2019-11-21扫码添加【考研班主任】

即可领取资料包

2023考研政治复习备考资料【珍藏版】

发布时间:2019-11-21扫码添加【考研班主任】

即可领取资料包

考研英语万能模板+必备词汇+范文

发布时间:2019-11-21扫码添加【考研班主任】

即可领取资料包

考研数学一、二、三历年真题整理

发布时间:2019-11-21扫码添加【考研班主任】

即可领取资料包

添加班主任领资料

添加考研班主任

免费领取考研历年真题等复习干货资料

推荐阅读

推荐阅读

湖北师范大学2026年考研复试科目参考书目

来源 : 湖北师范大学 2025-03-24 17:29:44 关键字 :

中国刑事警察学院2025年考研复试《治安案件查处》考试大纲 (2022年12月) Ⅰ 考查目标 要求考生了解、掌握查处治安案件的法

来源 : 中国刑事警察学院 2025-03-20 16:55:15 关键字 :

中国刑事警察学院2025年考研复试《总体国家安全观》考试大纲 (2024 年 12 月) Ⅰ 考查目标 要求考生具备国家安全治理的

来源 : 中国刑事警察学院 2025-03-20 16:51:28 关键字 :

中国刑事警察学院2025年考研复试《证据法学》考试大纲 (2024 年 12 月) Ⅰ 考查目标 证据法学要求考生具有全面了解、熟

来源 : 中国刑事警察学院 2025-03-20 16:50:07 关键字 :

中国刑事警察学院2025年考研复试《英语》考试大纲 (2023年12月) Ⅰ 考查目标 考生应掌握下列英语语言知识和技能: 一

来源 : 中国刑事警察学院 2025-03-20 16:48:37 关键字 :

资料下载

资料下载

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

新东方在线考研资料合集

下载方式:微信扫码,获取网盘链接

目录:

1.2013-2023年近10年政数英真题及解析PDF版(新东方)

2.2013-2023年专业课考试历年真题及解析PDF版

3.24考研复习备考资料大合集:大纲+备考资料+词汇书+考前押题+自命题

资料介绍:

1.2013-2023年近10年政数英真题及解析PDF版(新东方)

、

、

2.2013-2023年专业课考试历年真题及解析PDF版

3.24考研复习备考资料大合集

3.24考研复习备考资料:考研大纲

3.24考研复习备考资料:政数英备考资料+自命题真题

------------------

考研备考过程中,尤其是专业课部分,参考往年的考试真题,对于我们的复习有更好的帮助。北京大学考研真题资料都有哪些?小编为大家进行了汇总。

北京大学考研真题资料-公共课

北京大学考研真题资料-专业课

以上就是关于“北京大学考研真题资料下载(历年汇总)”的整理,更多考研资料下载,请关注微信获取下载地址。

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

扫码添加【考研班主任】

即可领取资料包

阅读排行榜

阅读排行榜

相关内容

相关内容